CS61C-Risc-V Processor Design

友情链接:MIPS指令结构

CPU

- Processor: active part of the computer that does all the work(data manipulation and decision-making)

- Datapath: portion of the Processor that contains hardware necessary to perform operations required by the Processor

- Control: portion of the Processor(also in hardware) that tells the Datapath what needs to be done

Building a Risc-V Processor

可以类比成状态机的设计。

将执行指令的过程拆解为多个小状态,方便设计。

- Stage 1: 指令的抓取(posedge)

- Stage 2: 指令的解码/寄存器的读取

- Stage 3: 执行-ALU

- Stage 4: 访问内存

- Stage 5: 写回到寄存器中(posedge)

How to Build a Datapath

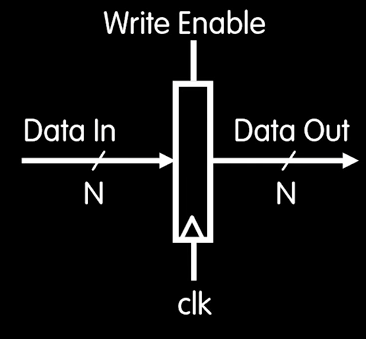

- 寄存器

- 写使能:为1时在posedge的时候更新为In

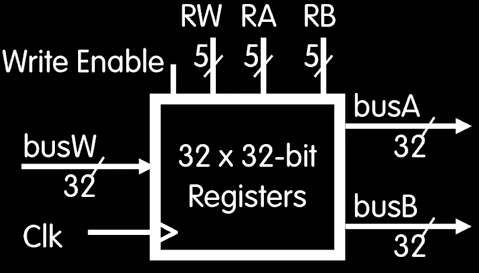

- 寄存器组(包含32个寄存器)

- RA用来选择放在busA的寄存器,RB同理

- RW用来选择要被执行写操作的寄存器(当写使能为1时且写入的数据由busW传递)

- 当执行读取操作时,寄存器组被视作一个组合逻辑电路(在输出前的延迟时间为乘坐”access time“

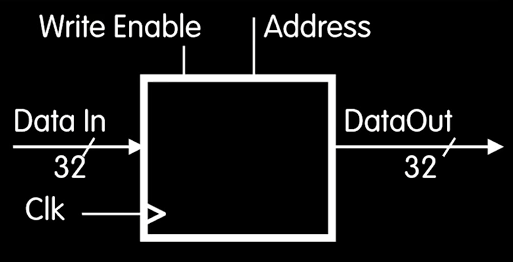

- 内存

- 对于读取:地址选择应该被放在Data Out的数据

- 对于写入:地址选择应该被Data In写入的内存(当写使能为1时)

- 读取操作与寄存器相同

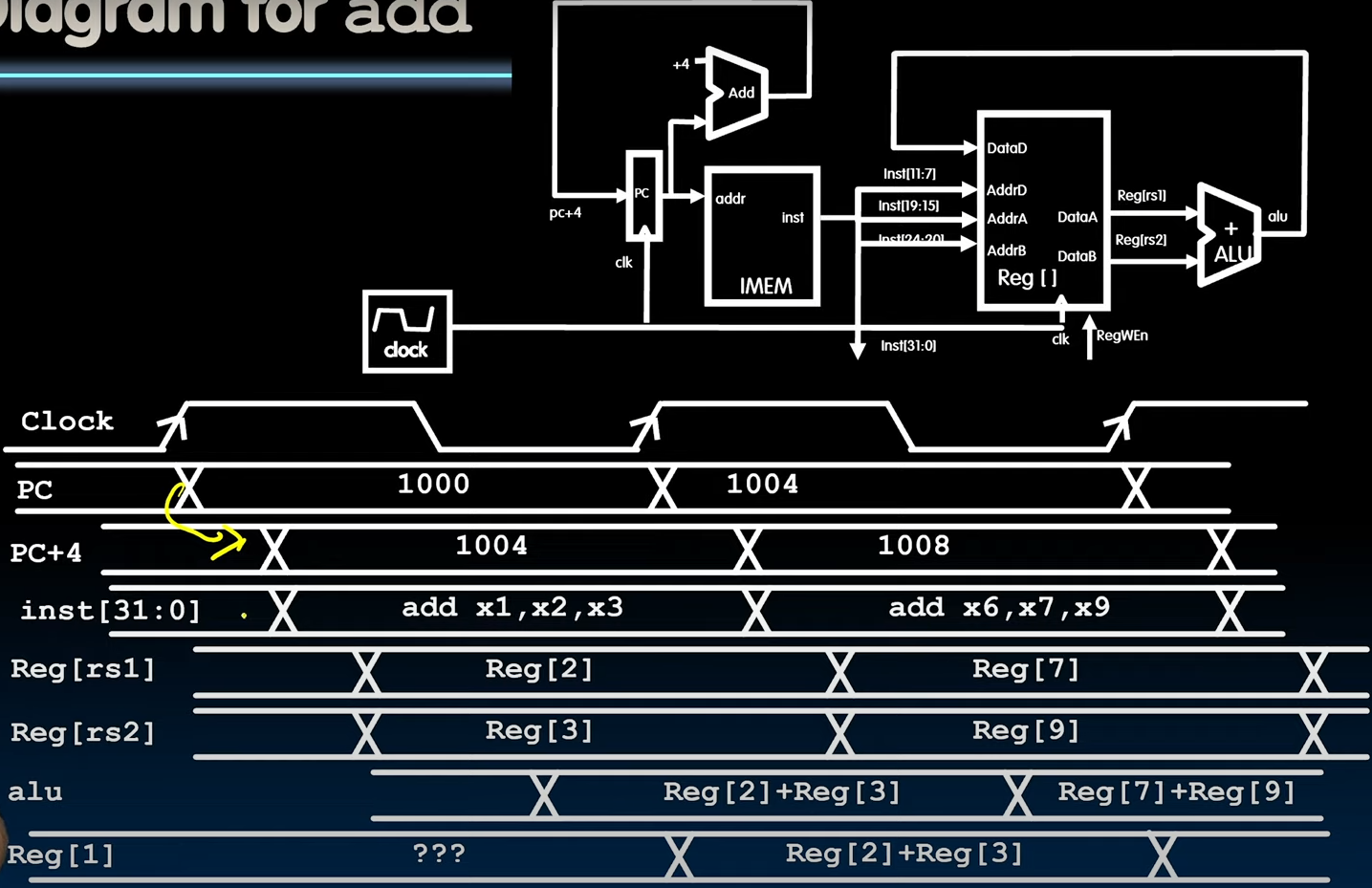

Datapath for add/sub

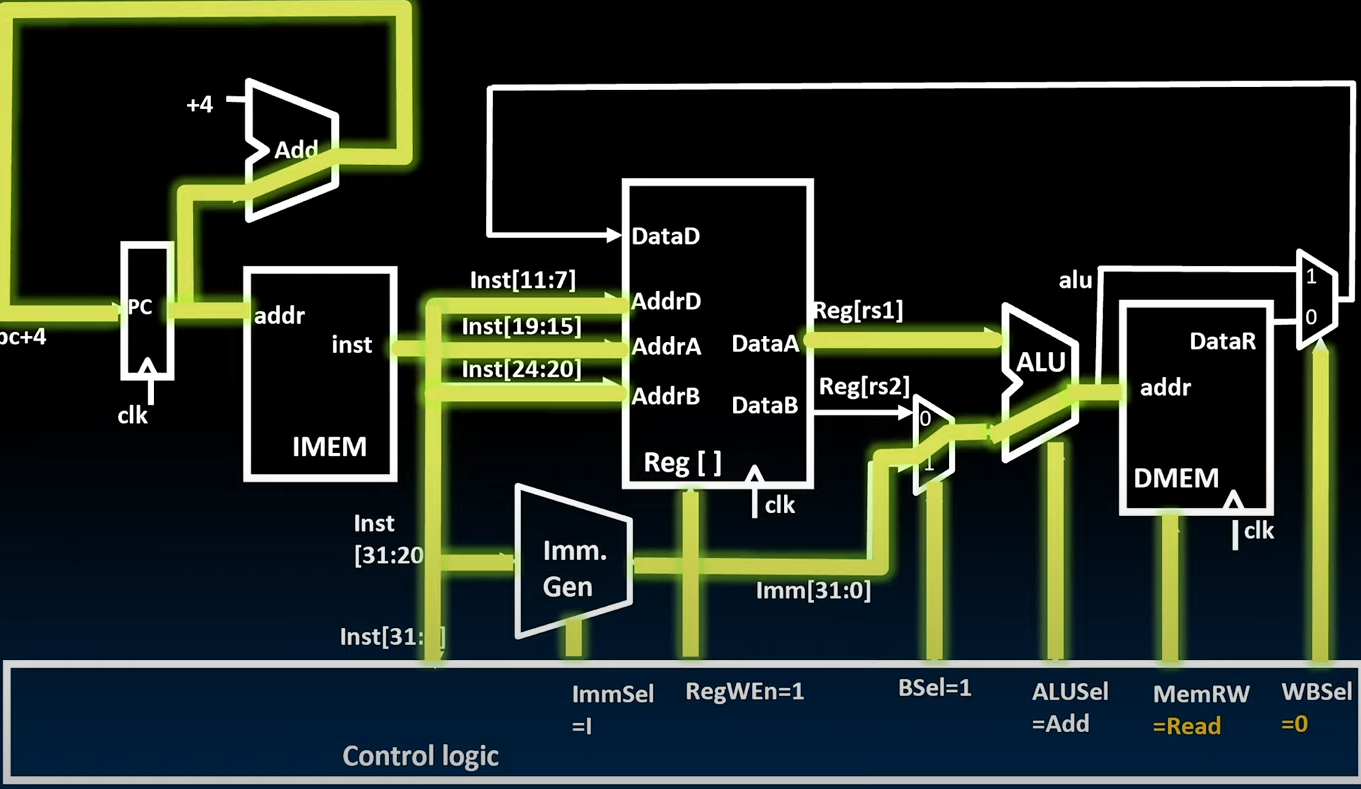

Datapath With Immediates

在I形指令中,立即数需要做扩展。而扩展的方式分为零扩展与符号扩展(根据编码的不同,扩展的方式也不相同)

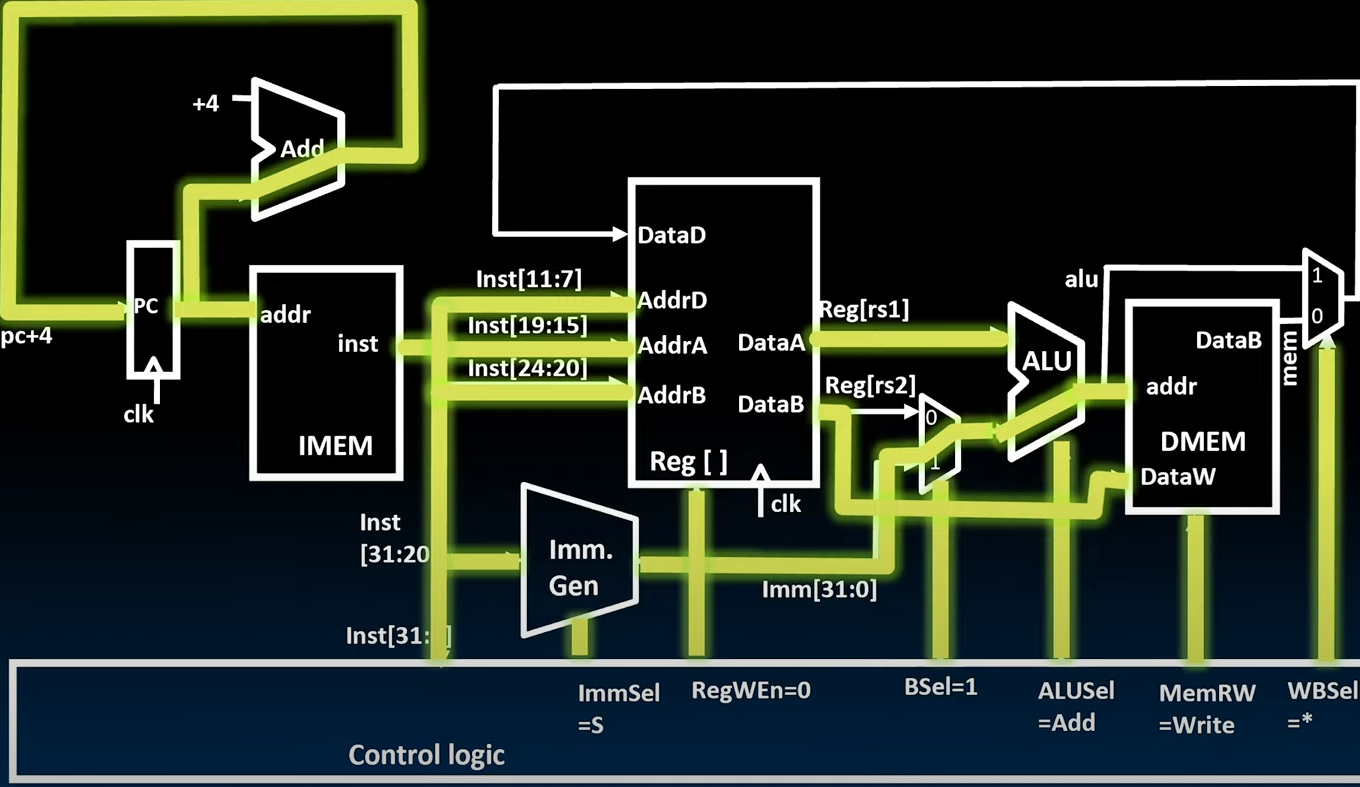

Datapath for Stores

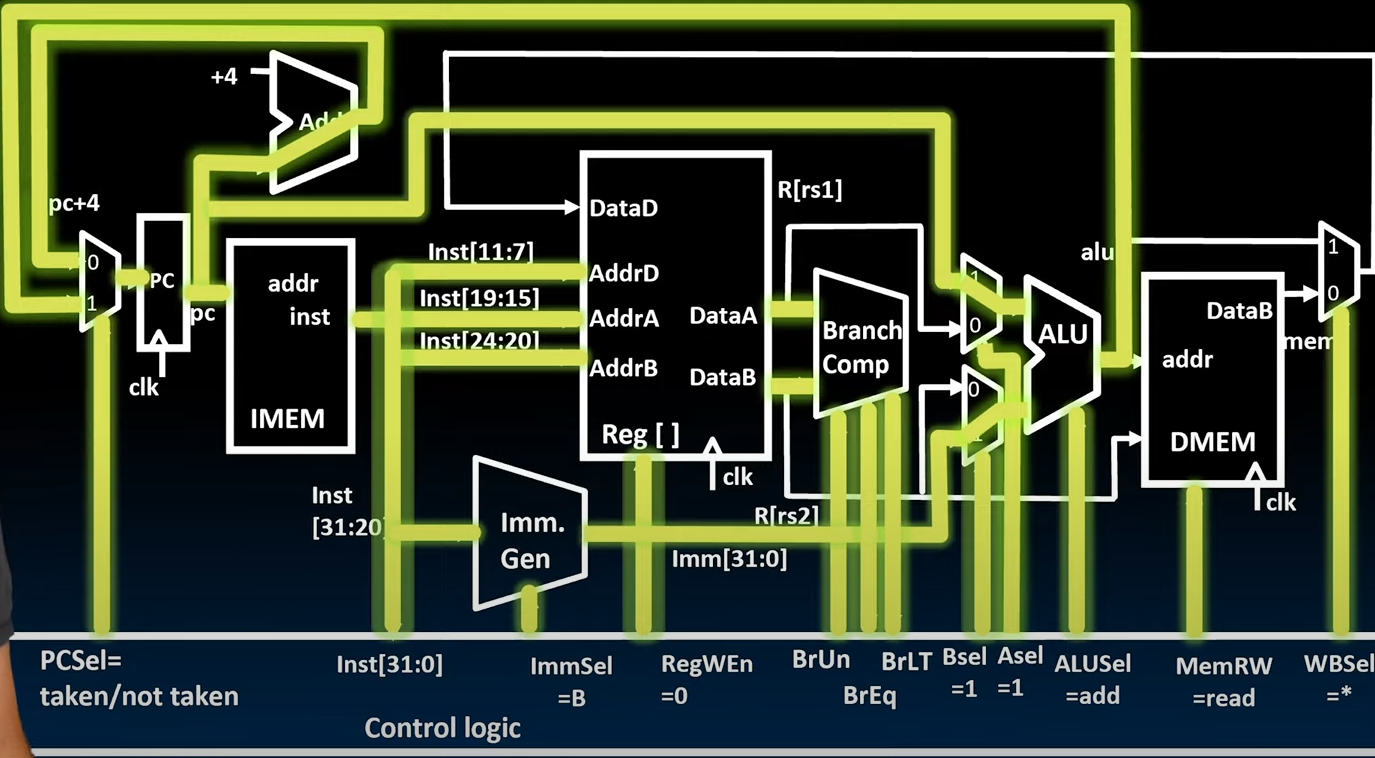

Implementing Branches

改变PC来实现分支:

- PC=PC+4(非分支)

- PC=PC+immediate(分支)

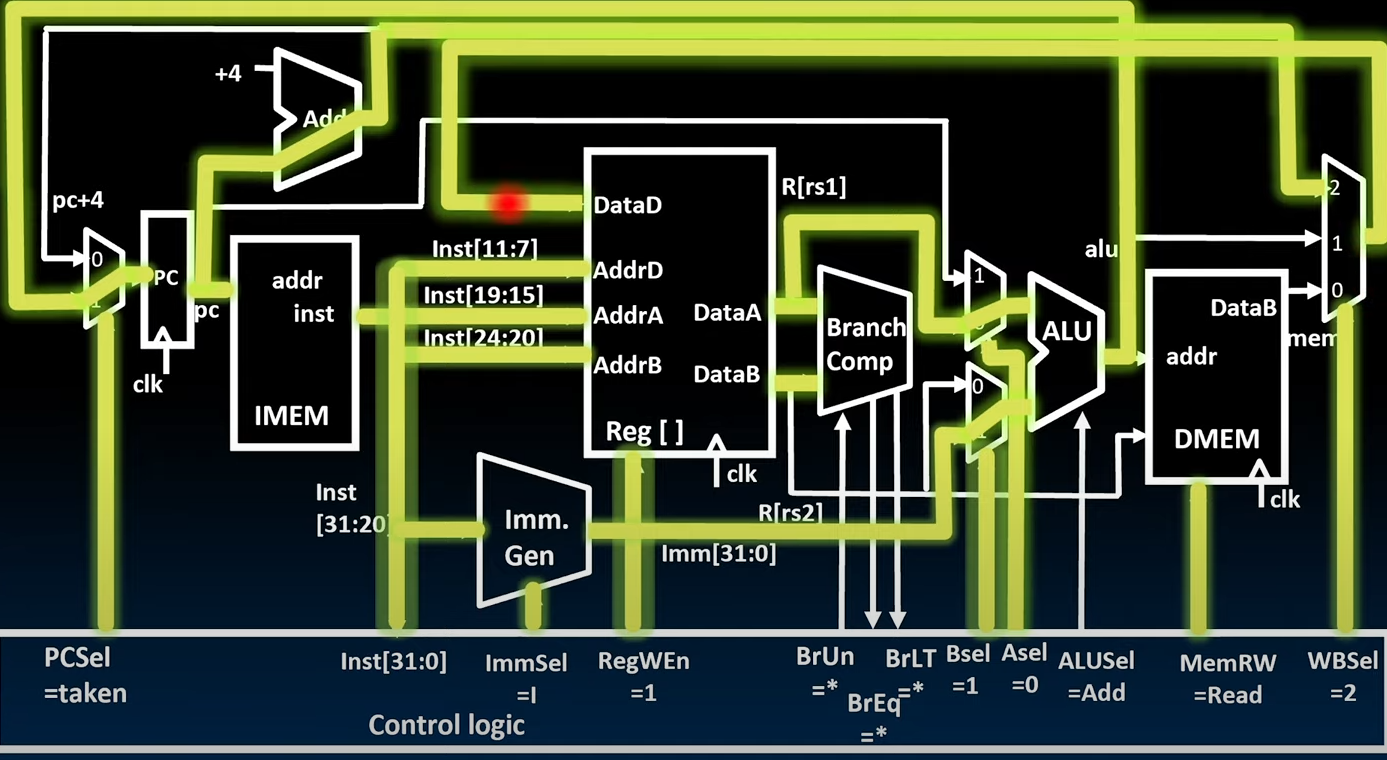

Adding JALR to Datapath

JALR是I形指令(Jump-And-Link-Register):

- JALR rd,rs,immediate

- 将PC+4写入rd

- 设置PC=rs1+immediate

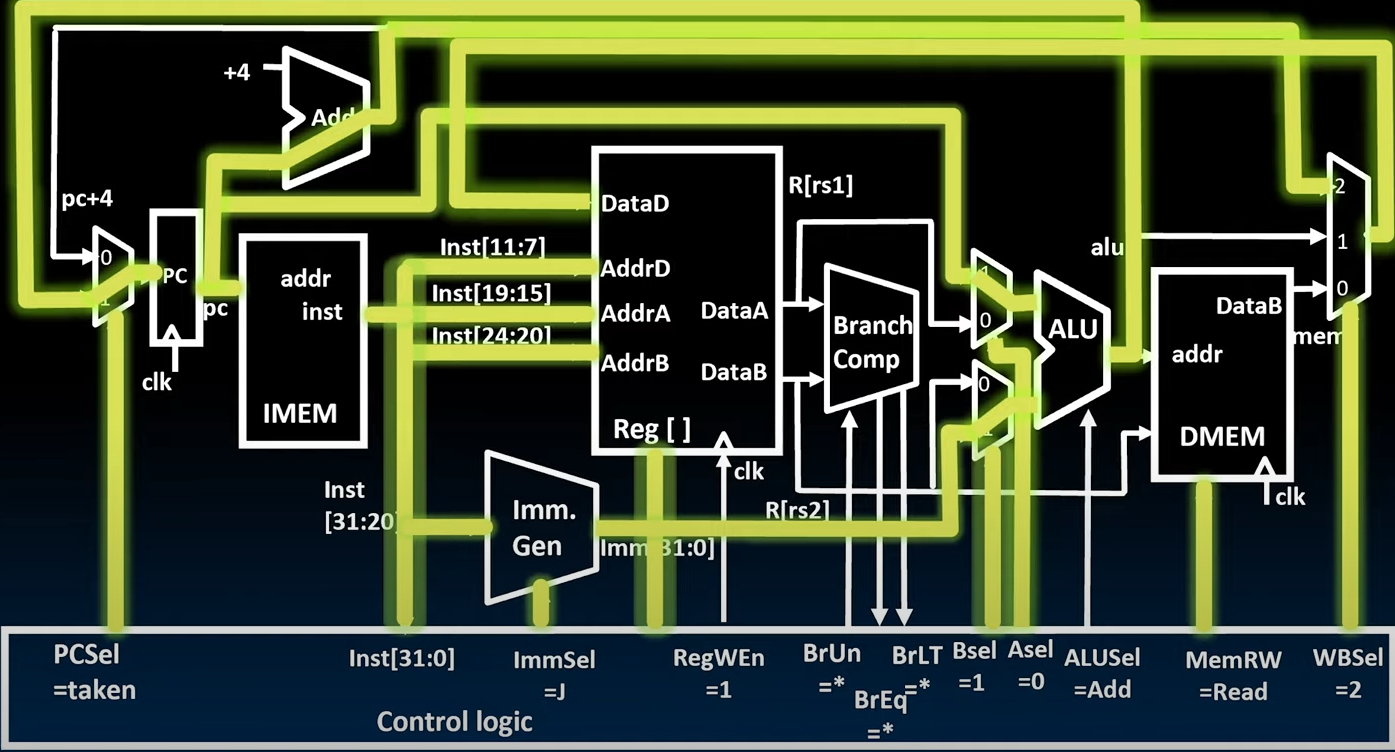

Adding JAL

J形式指令(与上面的JALR有一些类似)。不同的地方在于,PC=PC+offset(PC-relative jump)

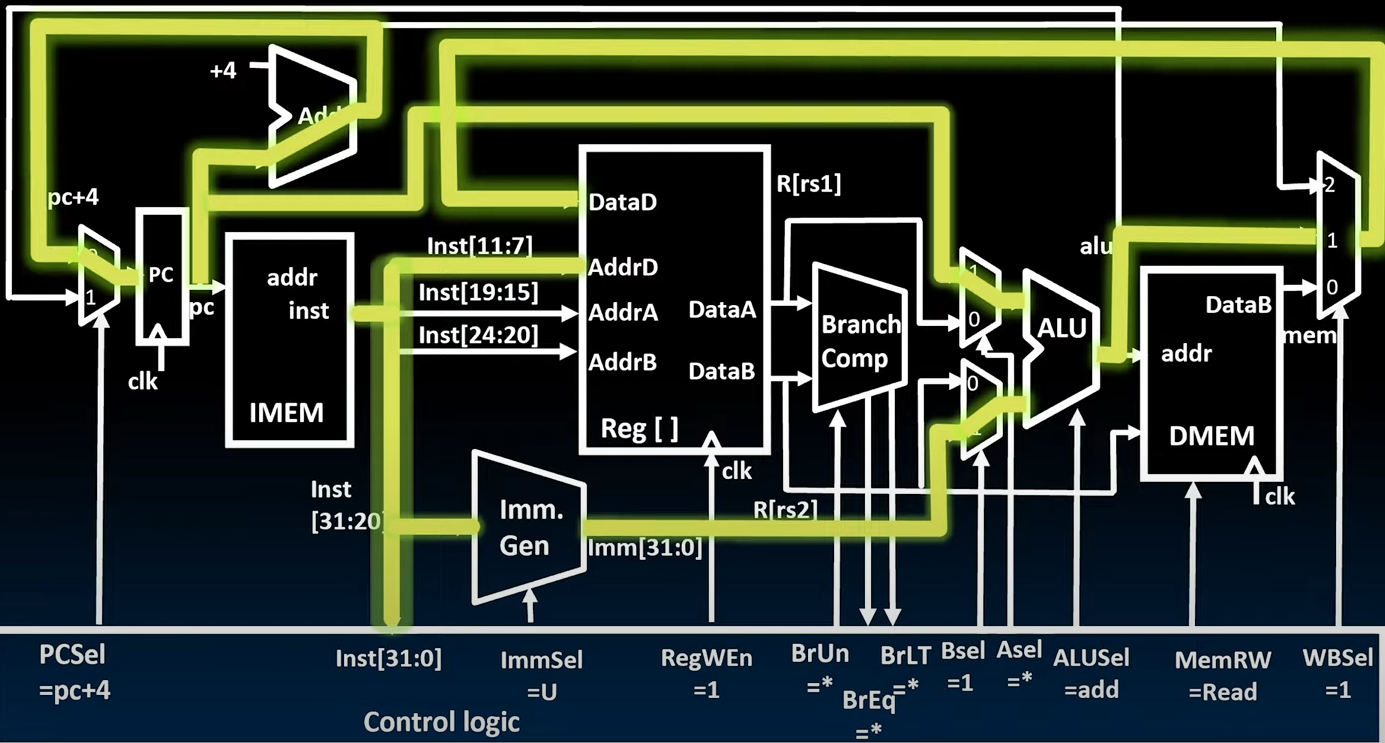

Adding U-Types

终于要结束了

我们来看最后一种类型的指令——U-Types.

- lui:load upper immediate

- auipc:add upper immediate to PC

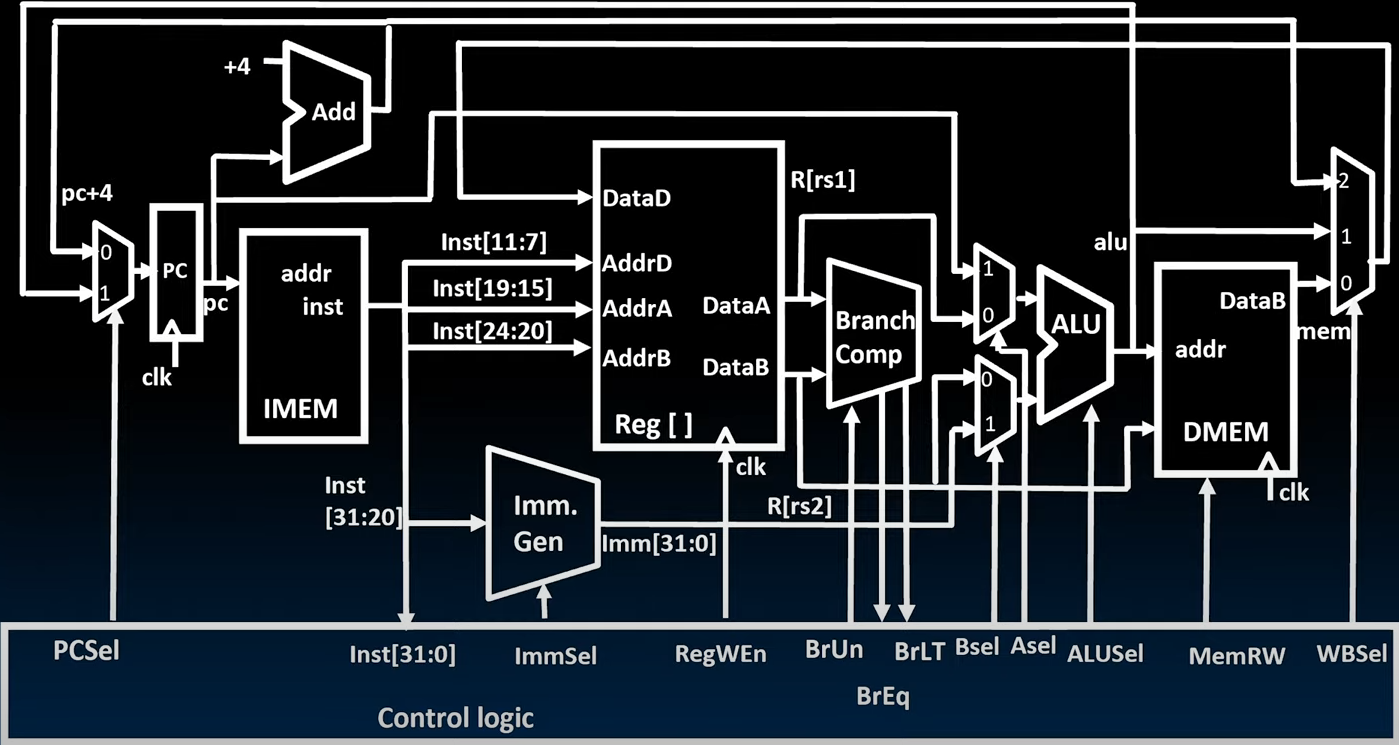

Recap Datapath!

到此,Datapath设计完成!

本文由作者按照

CC BY 4.0

进行授权